Decoders

어떤 동작을 할지 해석해주는 회로

c언어로 동작시 컴파일러가 기계어(11010011...)로 바꿔주는데 기계어 중에 특정 bit는 어떤 동작을 하는지 알려주는 instruction과 어떤 동작을 하는지 알려주는 instruction이 있다. 특정 비트는 대체로 앞 4자리로 add역할을 할지 load역할을 할지 등등 알려주는 instruction이며 이를 opcode(operation code)라 부른다.

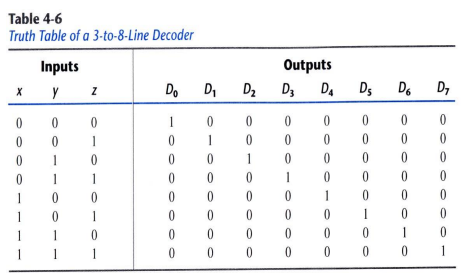

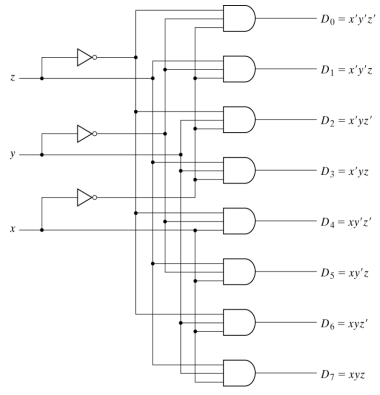

ex] 3 to 8 line decoder (3 in -> 2^3 output)

input에 따라 D에는 output이 한개로만 흐른다.

x,y,z에 input에 따라 어느 D를 활성화 할지 정하게 된다.

ex] 2 to 4 line decoder (2 in -> 2^2 output)

E는 enable로 decoder를 동작시킬지 말지 정하게 되고 E가 1이면 인버터에 의해 0이되어 A,B에 어떤 값이 들어오더라도 D는 모두 1이되어 Decoder역할을 못하게 한다. E가 0일때 A,B 값에 따라 0이 되는 지점을 찾아주는 Decoder역할을 하게 된다.

Combinational logic implementation: decoder와 OR gate를 이용하여 모든 연산을 만들 수 있다. 하지만 비효율적이라 사용하지는 않음.

full adder에서 1이 군대군대 나온다.

decoder와 or gate를 이용하여 adder gate를 만들 수 있다.

Encoder

Encoder와 반대 연산을 한다. 2^3 output ->2 input.

예로, 아날로그 통화 목소리를 2진수화(디지털화)할때 사용한다.

Multiplexer(mux)

많은 input line 중에 특정 input을 넣고싶을때 selection line을 정해서 특정 input만 출력해내는 역할

2^n 개의 input은 n개의 selection line을 갖습니다.

4 to 1 line mux

Quadruple 2 to 1 line mux

three state gate, c의 값에 따라 buffer가 신호를 전달할지 말지를 정하게 된다.

three state gates

Sequential circuits

Logic은 크게 combination과 sequential로 나눌 수 있음. 지금까지 combination logic을 살펴보았고 sequential logic을 살펴볼거임

combination은 input이 들어오면 바로 output이 나옴. 어떠한 값을 기억하는 logic이 없음

sequential logic은 time이라는 개념이 도입되어 어떤 gate가 적절히 loop back을 통해 값을 기억하는 logic이 있음

memory elements가 포함된 sequential circuit.

memory elements는 flip/flop(f/f)가 기본 단위이다. dram은 cpu밖에 존재.

f/f는 clk이라는 time개념이 도입되어 동작한다.

F/F에 대해 알아보기 전 Latches에 대해 알아보자.

Latches란 어떤 값을 keep할 수 있는 능력을 가진 논리 gate의 모음

SR Latches는 2개의 NOR gate로 이뤄져 S가 Q에 전달된다.

undefiend 상태는 오류상태이다.

S=1 R=0 일 때 동작

S=0 R=1 일 때 동작

(after S=0 R=1) S=0 R=0 일 때 keep

SR Latch를 NAND로도 구현할 수 있다. 이 때 R의 값이 Q에 전달된다.

S=0 R=0 일 때 undefiend 상태가 된다.

S=1 R=1 일 때 Keep